# Electronic Hardware Onboarding: Communication Protocols

### Introduction

#### <u>Agenda</u>:

- 1. Logic Levels

- 2. Pull Resistors

- 3. Push-Pull & Open-Drain

- 4. Parallel vs Serial

- 5. UART

- 6. SPI

- 7. I2C

- 8. SD/MMC

- 9. PWM

#### <u>Goal</u>:

Understand the various ways embedded digital components communicate with one another

### **Logic Levels**

#### <u>Intro</u>

- The binary ON (1) OFF (0) states of a digital circuits via voltage

- Different logic "levels" exists 5V, 3.3V, 1.8V referring to V<sub>DD</sub> value (Need logic level shifting chips to convert between levels)

#### **Thresholds**

- V<sub>DD</sub> Power supply voltage, max voltage

- V<sub>OH</sub> Output High, minimum output voltage for high state

- V<sub>IH</sub> Input High, minimum input voltage for high state

- V<sub>OL</sub> Output Low, maximum output voltage for low state

- V<sub>IL</sub> Input Low, maximum input voltage for low state

- GND Common voltage reference, lowest voltage

- Different per logic level! 5V, 3.3V, etc...

VDD 3.3V HIGH (1) 2.4V 2V ۷ін Floating-0.8V LOW (0) -0.5V GND

3.3V Logic Families (Based on 74LVT04 Hex Inverter)

### **Pull Resistors**

#### Pull-Up

• A resistor used to pull a line up to voltage supply

#### <u>Pull-Down</u>

• A resistor used to pull a line down to ground

#### Pin States

- <u>Active High</u>: A high signal actives the system or specific function

- <u>Active Low</u>: A low signal actives the system or specific function (*Pin may be show with line over name Ex:*  $\overline{CS}$ )

- <u>High Impedance</u>: A circuit that is not driven high or low and is floating, requires external circuit to change its state (*Impedance = Resistance + Reactance*)

- <u>Floating</u>: Undefined, achieved when pin isn't connected to V<sub>DD</sub> or GND (Unintentional floating circuits may behave unexpectedly)

#### <u>Note</u>

• Large resistors lead to weak pull-ups and pull-downs.

VDD

DATA1D

DATA2D

**Pull Down**

Pull Up

3.3k

DATA1

DATA2

3.3k

GND

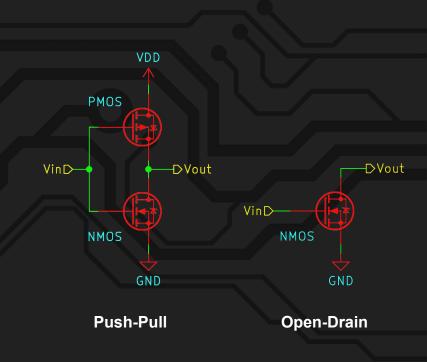

# Push-Pull & Open-Drain

How do output pins change from high to low?

#### Push-Pull

- Two transistors switch between load voltage and GND

- Commonly used for unidirectional lines (SPI, UART)

#### **Open-Drain**

- One transistors ties the output to GND

- An external resistor pulls the line high by default

- Commonly used for bidirectional lines (I2C)

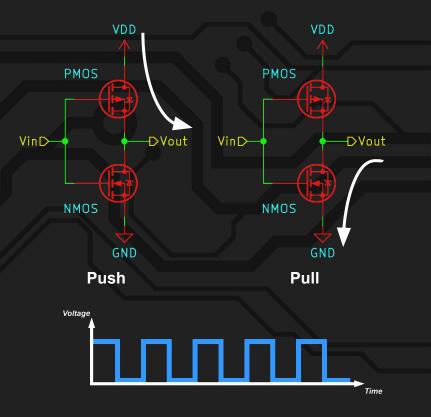

### **Push-Pull**

#### <u>Push</u>

- When the output pin is driven to 1 transistors

- "Sourcing current to the load"

#### <u>Pull</u>

- When the output pin is driven to 0 by the transistors

- "Sinking current from the load"

#### <u>Notes</u>

• Consistently driven ≈ better performance (Sharper rising edge slope)

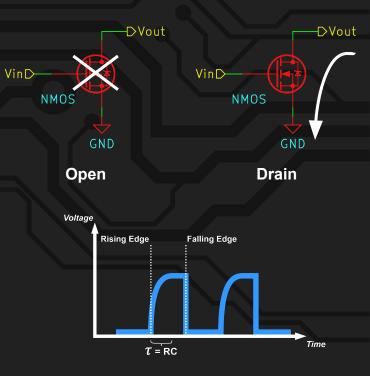

### **Open-Drain**

#### <u>Open</u>

- Line is left floating and <u>pulled up by external resistors</u>

- High impedance (Hi-Z) state

#### <u>Drain</u>

- When the output pin is driven to 0 by the transistors

- "Sinking current from the load"

#### **Rising Edge Slope**

- Wires naturally have capacitance so when combined with pull-up resistors it creates a low pass filter leading to curved rising edges (*Transistors in Push-Pull have less resistance so faster rising edges*)

- More resistance = Slower rising edge speeds & more noise

- Less resistance = More power consumption

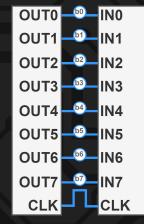

### **Parallel vs Serial**

#### Parallel

• Each bit in a piece of data is transferred simultaneously

#### Serial

- Each bit in a piece of data is transferred sequentially

- Slower than parallel but requires less hardware connections

#### Synchronous

- A common clock is shared amongst all devices on the data bus

- Requires at least one extra wire

#### Asynchronous

• Data is transferred without a shared common clock

#### **Baud Rate**

- The speed data is transferred over serial

- No set limit as long as both devices operate at the same rate

- Standard Rates:

- 9600, 1200, 2400, 4800, 19200, 38400, 57600, 115200

**Synchronous Parallel**

### **Serial Frames**

#### **Data Chunk**

- The section where actual data is sent

- Variable length, depends on protocol

#### Synchronization

- <u>Start</u>: A flag used to indicate a new packet

- End: A flag used to indicate the end of a packet

#### Address (Sometimes)

• Data to indicate destination on a multi-device shared bus

#### Parity

• Low level error checking

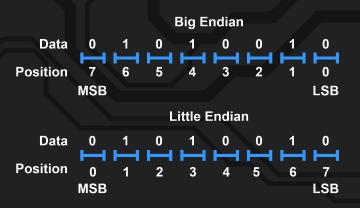

#### Endianness

- The order bits are sent

- <u>Big-Endian</u>

- Most Significant Bit (MSB) sent first

- MSB stored at smallest memory address

- <u>Little-Endian</u>

- Least Significant Bit (LSB) sent first

- LSB stored at smallest memory address

| Start Data | Parity End |

|------------|------------|

|------------|------------|

### UART: Universal Asynchronous Receiver/Transmitter

#### **Protocol Signals**

- <u>TX</u>: Transmit

- <u>RX</u>: Receive

#### **Features**

- Asynchronous

- Direct connections

- Full-duplex (TX & RX simultaneously)

#### **Common Errors**

- $TX \rightarrow RX \text{ not } TX \rightarrow TX$

- Baud rate mismatch

#### Implementation

- Converts between serial and parallel (Internally)

- May use first-in-first-out (FIFO) buffer to store data

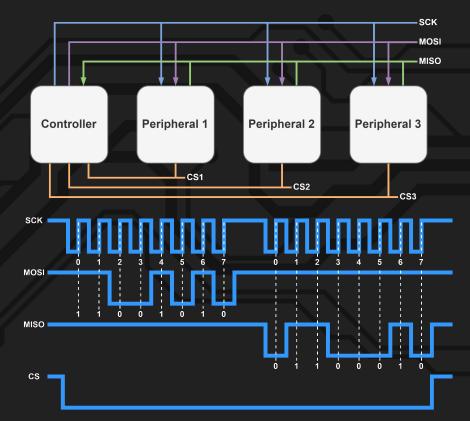

# **SPI: Serial Peripheral Interface**

#### **Protocol Signals**

- <u>SCK</u>: Serial Clock

- <u>MOSI</u>: Master Out Slave In

- <u>MISO</u>: Master In Slave Out

- <u>CS</u>: Chip Select

#### Features

- One controller many peripherals

- Many different speeds depending on hardware

- Extra data line versions (Octo-SPI & Quad-SPI)

- Synchronous

- Full-duplex

#### **Chip Select**

- Turns on peripheral

- Only one active peripheral

- Active low

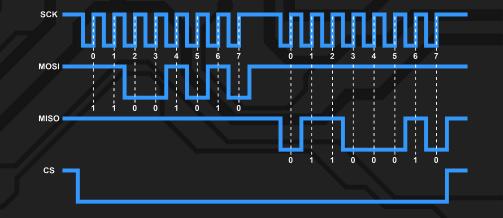

# **SPI: Serial Peripheral Interface**

#### Implementation

- Very simple implementation with shift register

- Single controller that generates clock

- Data sampled on either rising or falling edge (Check datasheet)

#### **Advantages**

- Can be very fast

- Supports multiple peripherals

- Simpler internal implementation

#### Disadvantage

- Requires more wires (CS line per peripheral)

- The controller must control all communications

- Peripherals can't communicate with each other

### SPI: BNO086 Example

| CEVA | ⊡hi | llcrestlabs.        |                                | BNO08X Data Sheet                                                                          | Schematic        | IMU 9DOF                                                                                  | +3V3                                                                                                       |

|------|-----|---------------------|--------------------------------|--------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 5    | PS1 |                     | Input                          | Protocol Select pin 1                                                                      |                  | BNO086                                                                                    | 1                                                                                                          |

| 6    | PS0 | /WAKE               | Input                          | Protocol Select pin 0, also<br>used to wake processor in SPI<br>mode                       |                  | R101                                                                                      | U103 M 🕅                                                                                                   |

| 17   | SA0 | /H_MOSI             | Input                          | Lower address bit of device<br>address. In <mark>SPI mode, data</mark><br>input            |                  | 10k<br>BN0086_CSD                                                                         |                                                                                                            |

| 18   | H_C | SN                  | Input                          | SPI chip select, active low                                                                |                  | SPI_MOSID                                                                                 | 17 H SAO MOSI ENV SCI 15                                                                                   |

| 19   | H_S | CL/SCK/RX           | Bidirectional                  | Host Interface I <sup>2</sup> C clock, <mark>SPI</mark><br>clock or UART RX                | Pin Descriptions | SPI_SCKD<br>SPI_MISOC                                                                     | 19<br>H_SCL/SCK/RX<br>20<br>H_SDA/H_MISO/TX<br>4                                                           |

| 20   | H_S | DA/H_MISO/TX        | Bidirectional                  | Host Interface I <sup>2</sup> C data, <mark>SPI</mark><br><mark>data out</mark> or UART TX | - 17/ 3          |                                                                                           |                                                                                                            |

|      |     |                     |                                |                                                                                            |                  | BN0086_RESETD                                                                             | 11 NRST XOUT32/CLKSEL1                                                                                     |

|      | PS0 | BNO08X<br>(BOOTN=1) | BNO08X<br>bootloade<br>(BOOTN= |                                                                                            | ation            | BN0086_BOOTD                                                                              | 4     BOOTN     XIN32     27       5     PS1     PS0/WAKE     CAP     9       6     PS0/WAKE     CAP     9 |

| 0    | 0   | I <sup>2</sup> C    | I <sup>2</sup> C               |                                                                                            |                  |                                                                                           | N S BN0086                                                                                                 |

| 0    | 1   | UART-RVC            | Reserved                       |                                                                                            |                  |                                                                                           |                                                                                                            |

| 1    | 0   | UART                | UART                           |                                                                                            |                  | Clock Select Pins<br>CLKSELO Low = External Cry                                           | estal BNO086                                                                                               |

| 1    | 1   | SPI                 | SPI                            |                                                                                            |                  | CLKSELO Low = External Cry<br>CLKSELO High = Internal Clu<br>(Internal Clock Pin 27 and 2 | ock                                                                                                        |

|      |     |                     |                                | and the                                                                                    |                  | L                                                                                         |                                                                                                            |

"Single chip 9 axis sensor with embedded sensor fusion that enables rapid development of sensor-enabled robotics, AR, VR, and IoT devices." - CEVA

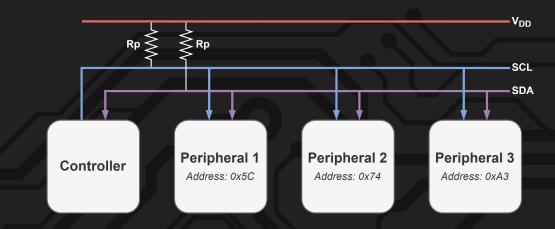

#### **Protocol Signals**

- <u>SDA</u>: Bidirectional data

- <u>SCL</u>: Clock

#### Modes

- Original: 100kHz

- Fast-mode: 400kHz

- Fast-mode plus: 1MHz

- High-speed mode: 3.4MHz

- Ultra-fast mode: 5MHz

- Custom speeds: 0kHz to 5MHz

#### **Pull-Up Resistors**

- Open drain, pull up resistors required for all signals

- 4.7kΩ is good starting point

- Adjust down as needed

- Datasheet may have recommendations

#### **Multiple Controllers**

- Multiple controllers can share a bus (SDA/SCLK) and talk to all peripherals

- Controllers can't talk to each other

- Controllers must take turns sharing bus

#### Addresses

- 7-bit (112 Devices)

- 10-bit (1008 Devices)

- 10b & 7b devices can coexist

#### SMBus

- System Management Bus

- I2C but more strict timing

- 10kHz to 100KHz only

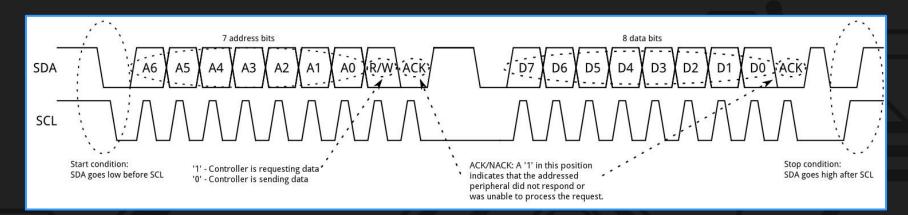

#### **Start Condition**

- Controller starts address frame by leaving SCL high and pulls SDA low

- All peripherals on alert

- Controller that pulls SDA low first wins in shared bus

#### 7-bit Address Frame

- Always sent first in new communication

- 7-bit Address (MSB first)

- Last bit is Read/Write (1 = Read, 0 = Write)

#### **Data Frame**

- Occur after address frames

- Controller continues sending clock pulses at regular intervals

- Number of data frames arbitrary

#### Acknowledge

- 9th bit of every frame

- Error checking

- NACK (1) = Not Acknowledged

- ACK (0) = Acknowledged

#### Acknowledge Steps

- 1. Receiving device given control of SDA

- 2. If receiving device doesn't pull SDA low before the 9th CLK pulse then transmission halts

(Failure response decided by system code)

#### **Stop Condition**

- SDA goes high after SCL

- During normal data writing operation, the value on SDA should not change when SCL is high, to avoid false stop conditions.

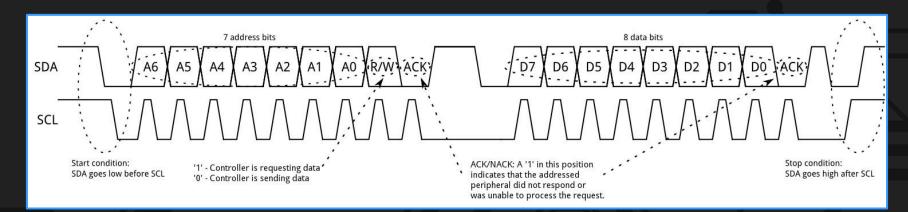

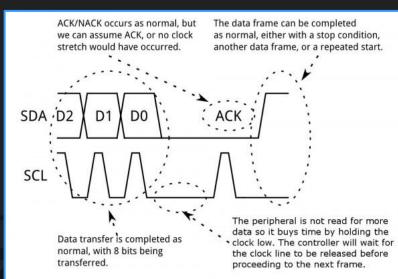

#### **10-bit Address Frames**

- <u>1st Frame</u>

- "11110" Specific flag for 10-bit addresses

- A9/A8 Address bits

- Read/Write bit (1 = Read, 0 = Write)

- Acknowledge bit from all devices that match A9 and A8 address bits

- 2nd Frame

- A7...A0 Address bits

- Acknowledge bit from specific device

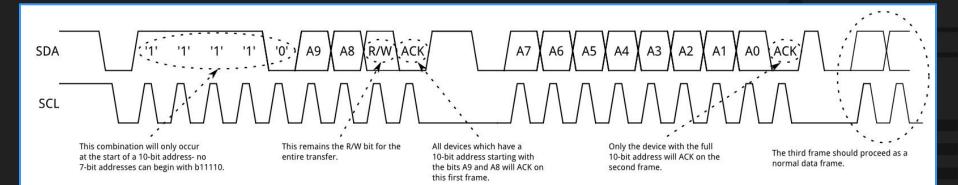

#### **Clock Stretching**

- Current controller controls clock

- Peripheral can pull clock low to delay the controller sending more data

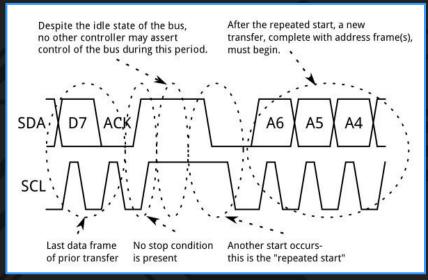

#### **Repeated Start Condition**

- Controller needs to continuously send data larger than 7 bits

- Don't send stop condition between frames

- Resends start condition

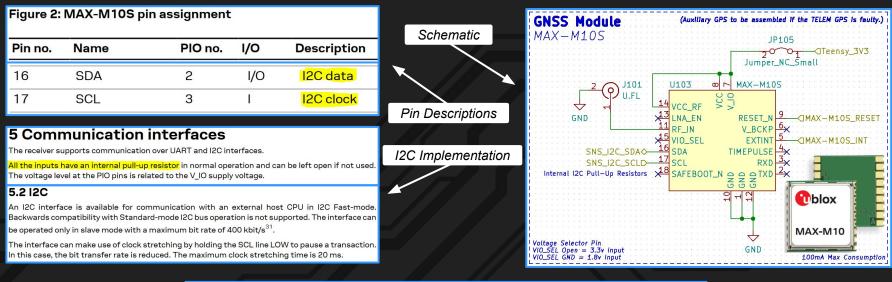

# I<sup>2</sup>C: MAX-M10S Example

<sup>31</sup> External pull-up resistors may be needed to achieve 400 kbit/s communication speed, as the internal pull-up resistance can be very large.

Global Navigation Satellite System (GNSS) = Global Positioning System (GPS, US Version)

"Ultra-low-power GNSS receiver for high-performance asset-tracking devices. Less than 25 mW power consumption without compromising GNSS performance. Maximum position availability with concurrent reception of 4 GNSS." - ublox

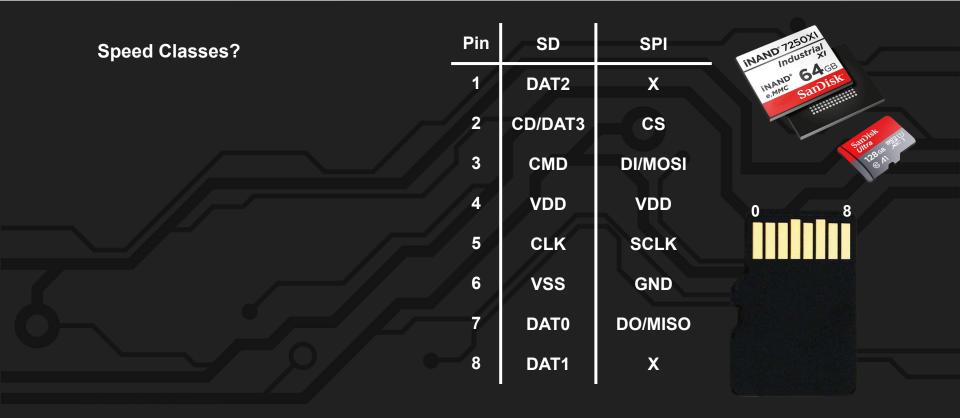

### SD/MMC: Secure Digital / Multi-Media Card

| MicroSD Card                                                                                                         | Pin | SD      | SPI     | INAND 7250XI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------|-----|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Can either be used with SD or SPI interfaces</li> <li>Sometimes slots come with card detect pins</li> </ul> | 1   | DAT2    | x       | INAND GAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>Can be left floating if unused</li> </ul>                                                                   | 2   | CD/DAT3 | CS      | Title Old and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| eMMC     Embedded multi-media card                                                                                   | 3   | CMD     | DI/MOSI | Tilling of the second s |

| <ul> <li>Like a MicroSD card but soldered in place</li> <li>May have up to 8 data lanes</li> </ul>                   | 4   | VDD     | VDD     | 1 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                      | 5   | CLK     | SCLK    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                      | 6   | vss     | GND     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                      | 7   | DAT0    | DO/MISO |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                      | 8   | DAT1    | x       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                      |     |         |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

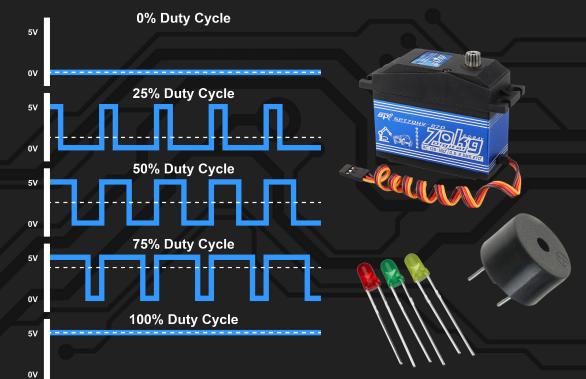

## **PWM: Pulse Width Modulation**

#### **Protocol Signals**

• <u>PWM</u>: Pulses

#### **Characteristics**

- Frequency: Rate of oscillation

- Duty Cycle: Percentage of "ON" time

<u>Example</u>: An LED with a 20% duty cycle at 1 Hz will be obvious that it's turning on and off to your eyes, meanwhile, a 20% duty cycle at 100 Hz or above will just look dimmer

#### Usages

- Servo Motors

- Piezo Buzzers

- LED Dimmers

- And much more!

*PWM emulates an analog signal by controlling the average power output. Faster frequencies produce a better analog appearing signal.*

### **SD/MMC:** Secure Digital / Multi-Media Card

### **Balanced and Differential**

- 1. <u>Text</u>

- 2. <u>https://www.allaboutcircuits.com/technical-articles/the-why-and-how-of-differential-signaling/</u>

- 3. <u>https://forum.headphones.com/t/single-ended-balanced-differential-w</u> <u>hat-it-means/3571</u>

Illinois Space Society - Spaceshot Avionics - 2023

### **Signal Names**

#### Names

۲

- SDO Serial Data Out. An output signal on a device where data is sent out to another SPI device.

- SDI Serial Data In. An input signal on a device where data is received from another SPI device.

- CS Chip Select. Activated by the controller to initiate communication with a given peripheral.

- PICO (peripheral in / controller out). For devices that can be either a controller or a peripheral; the signal on which the device sends output when acting as the controller, and receives input when acting as the peripheral.

- POCI (peripheral out / controller in). For devices that can be either a controller or a peripheral; the signal on which the device receives input when acting as the controller, and sends output when acting as the peripheral.

- SDIO Serial Data In/Out. A bi-directional serial sign

- SCK Serial Clock. The clock for the bus generated by the controller.

- MOSI Master Out Slave In

- MISO Master In Slave Out

- SS Slave Select

- MOMI Master Out Master In

- SOSI Slave Out Slave In

Protocol Signals 5V: Voltage supply +D: Data positive -D: Data negative ID: On-The-Go (OTG) identification GND: Ground

<u>Pro/Cons</u> <u>Simple to implement</u> <u>Power and data</u> <u>Slower than other USB types</u> <u>Special PCB routing considerations</u> (Differential pair)

USB OTG ID Some devices have flexible dual roles Negotiates between two devices to determine the host and peripheral device

<u>Note</u>: Electrostatic Discharge (ESD) chips are commonly used to protect USB connectors and devices when connecting and disconnecting.

# **Bit Banging**

#### **Bit-Banging**

A "term of art" for any method of data transmission that employs software as a substitute for dedicated hardware to generate transmitted signals or process received signals

### **Further Reading**

1i101i10, and Big6Big6. "Difference between Open Drain and Push-Pull Modes." *Electrical Engineering Stack Exchange*, 18 May 2022, electronics.stackexchange.com/questions/620150/difference-between-open-drain-and-push-pull-modes. Accessed 29 Dec. 2023. bri\_huang. "Logic Levels." SparkFun, learn.sparkfun.com/tutorials/logic-levels/all. Accessed 29 Dec. 2023. jimblom. "Serial Communication." SparkFun, learn.sparkfun.com/tutorials/serial-communication. Accessed 29 Dec. 2023. JordanDee. "Pulse Width Modulation." SparkFun, learn.sparkfun.com/tutorials/pulse-width-modulation. Accessed 29 Dec. 2023. MikeGrusin. "Serial Peripheral Interface." SparkFun, learn.sparkfun.com/tutorials/serial-peripheral-interface-spi. Accessed 29 Dec. 2023. Seidle, Nathan. "A Redefinition of SPI Signal Names." SparkFun, www.sparkfun.com/spi signal names. Accessed 29 Dec. 2023. SFUptownMaker. "I2C." SparkFun, learn.sparkfun.com/tutorials/i2c/all. Accessed 29 Dec. 2023. Stoyanov, Yasen. "Open Drain Output vs. Push-Pull Output." Open4Tech, 18 May 2019, open4tech.com/open-drain-output-vs-push-pull-output/.

Valdez, Jonathan, and Jared Becker. "Understanding the I2C Bus." *Texas Instruments*, <u>www.ti.com/lit/an/slva704/slva704.pdf</u>. Accessed 29 Dec. 2023.

# **Further Reading**

#### Works Cited:

- 1. https://learn.sparkfun.com/tutorials/logic-levels/all

- 2. https://electronics.stackexchange.com/questions/620150/difference-between-open-drain-and-push-pull-modes

- 3. https://open4tech.com/open-drain-output-vs-push-pull-output/

- 4. https://www.sparkfun.com/spi\_signal\_names

- 5. https://learn.sparkfun.com/tutorials/i2c/all

- 6. https://www.ti.com/lit/an/slva704/slva704.pdf

- 7. https://learn.sparkfun.com/tutorials/serial-peripheral-interface-spi

- 8. https://learn.sparkfun.com/tutorials/serial-communication

- 9. https://learn.sparkfun.com/tutorials/pulse-width-modulation

- 10. https://www.ti.com/lit/an/sloa101b/sloa101b.pdfhttp://www.electroniccircuitsdesign.com/pinout/sd-microsd-card-pin out.html

- 11. https://www.circuitstate.com/tutorials/interfacing-catalex-micro-sd-card-module-with-arduino/

- 12. https://www.kingston.com/unitedkingdom/en/blog/personal-storage/memory-card-speed-classes

- 13. https://www.integralmemory.com/articles/memory-cards-understanding-the-labels/

- 14. https://www.banggood.com/fr/SPT-Servo-SPT70HV-320-70KG-Large-Torque-Metal-Gear-Digital-Servo-For-RC-Robot -RC-Car-p-1577512.html?cur\_warehouse=CN

- 15. https://www.pcboard.ca/minipiezo-buzzer